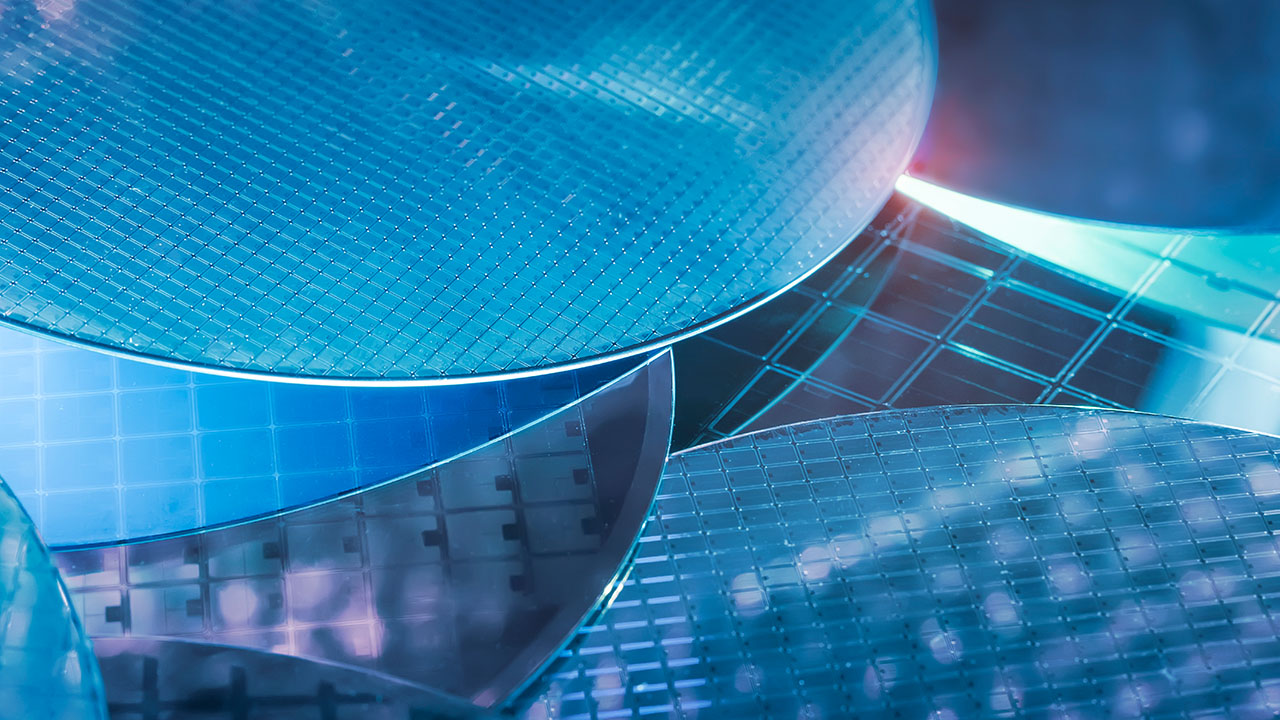

Siemens Digital Industries Software today announced a major upgrade in its partnership with Samsung Foundry to expand the certification of electronic design automation tools across multiple advanced process nodes and jointly deliver next-generation innovative solutions for cutting-edge design challenges.

The collaboration covers FinFET and MBCFET processes (SF2/SF2P) from 14nm to 2nm, and Siemens' full EDA portfolio – including key tools such as Caliber, Solido, and Aprisa – has been certified at the appropriate nodes, providing customers with strong tool support and technical support for the development of next-generation semiconductor products.

"We are excited to further deepen our collaboration with Siemens, which continues to expand the value of its technologies in the Samsung foundry ecosystem and continue to provide comprehensive support for our latest advanced process nodes." ——Sungjae Lee, Vice President of Samsung Electronics' foundry PDK development team, said. "In addition to completing the certification of our EDA tools, we have joined forces with Siemens to deliver a number of joint innovations in key areas, including power integrity verification, silicon photonics, analog mixed-signal reliability verification, and more, which will help our customers stand out in a highly competitive global marketplace."

Pictured: Siemens Digital Industries Software and Samsung Foundry deepen cooperation

A number of EDA tools have passed the advanced process node certification

Siemens EDA's three core product lines have recently completed the certification of several of Samsung's advanced process nodes, including the 14nm to 2nm nodes (SF2/SF2P) that support FinFET and MBCFET technologies. These include:

1. Calibre nmPlatform: For chip-level verification signoff with efficient and accurate DRC/LVS capabilities. At the same time, Calibre DesignEnhancer can automatically complete layout optimization based on Samsung process rules, improving design quality and manufacturability.

2. Solido Simulation Suite: includes the Solido SPICE and Analog FastSPICE (AFS) platforms, enabling high-precision simulation verification of analog, RF, and 3D IC designs; Solido LibSPICE supports batch SPICE validation of IP libraries and storage cells. The platform also supports the Open Model Interface (OMI) standard model interface, which fully supports aging modeling and reliability analysis from 14nm to 2nm nodes.

3. Aprisa Digital Implementation Tool: With highly consistent verification results and full support for the design rules and features of Samsung's process platform, Aprisa Digital Implementation Tool can help customers quickly optimize place-and-route and timing performance during the digital chip implementation phase.

In addition, the Caliber and Solido tools have been certified for Samsung's latest FD-SOI (Silicon-on-Insulator) process, including 18FDS and above.

Co-Innovation: Focus on 3D ICs and system-level design challenges

This collaboration is not limited to the certification of traditional EDA tools, but also focuses on the key problems in the current chip design field. Siemens and Samsung have joined forces to develop next-generation joint solutions for multiple challenging areas such as 3D IC architecture, power integrity analysis, silicon photonics, circuit aging and reliability verification.

"IC design and manufacturing are becoming more complex, and close collaboration between industry partners is critical to meeting the evolving needs of our customers." - Juan C. Rey, senior vice president of the Siemens Caliber product line. "Our close collaboration with Samsung is a testament to this spirit of collaboration in driving many cutting-edge technological advancements, including 3D ICs. With this new set of certifications and innovative design methodologies, we are injecting new impetus into our customers' global competition.”

This deepening cooperation not only demonstrates the adaptability of EDA tools to advanced process nodes, but also demonstrates the strategic collaboration between Siemens and Samsung in leading the evolution of chip design technology. Through the continuous expansion of the technology ecosystem and highly integrated solutions, the two parties will continue to provide an efficient, secure and scalable development platform for global chip design enterprises, helping them accelerate breakthroughs in key directions such as intelligence, low power consumption and high computing power.